|

The total current of transistor Q now becomes (I 1 + 0.84N) mA where I 1 say 2.4 mA is the current through R C. The load current is referred to as the standard load current.

Then the current in this diode is I = (5-0.8) volts 4k-ohms = 0.84 mA, where 0.8 volt is the voltage of point 0. Let us assume that all the input diodes in the following stages are high except the one says input M 1 driven by transistor Q. Thus, when Q is in saturation (Y = 0), the input current I of the following stage adds to the collector current of transistor Q. The output transistor Q thus functions as a sink for the current in the inputs to the gates it drives. Thus, the last row of the truth table of figure 1(b) is satisfied.įan Out: In actual practice, the NAND gates of figure 4 drive several, say N similar gates. Transistor Q is now driven into saturation and the output voltage at Y then falls to its low state (state 0). Voltage V K at point k rises towards V CC resulting in finite base current I B. Next, consider the situation when all the inputs are high (in state 1) corresponding to the last row of truth table in figure 1(b). The first three rows in the truth table of figure 1(b) are thus satisfied by the logic. Hence, diodes D 4 and D 5 are nonconducting, resulting in zero base current I B. Then the corresponding diodes/diodes conduct and voltage V K at point K is low. Let at least one out of the various inputs to the AND gate be low (in 0 state).

Figure (5) shows the resulting IC positive DTL NAND gate. The circuit is further modified for use of a single 5-volt supply instead of three separates 12-volt supplies. Hence, the NAND gate of figure 1 when fabricated in the IC form is modified by (i) eliminating the capacitor C 1 (ii) reducing greatly the values of resistors and (iii) using diodes and transistors to replace resistors wherever possible. On the other hand, diodes and transistors may be fabricated most economically using IC technology. However, using IC technology, large value resistors (>30 K-OHMs) and large value capacitor (>100 pF) cannot be fabricated economically. IC technology is most properly used for fabricating logic gates. Integrated Circuit Positive Diode Transistor Logic (DTL) NAND Gates Hence, NAND gates and NOR gate are often referred to as Universal gates. It follows, therefore, that any desired logic may be performed by repeated use of NAND gates alone or nor GATES ALONE. Using De Morgan’s Law, it may be shown that irrespective of the hardware used, a positive NAND gate is also a negative NOR gate while NAND gate is also a positive NOR gate.Īny logic may be performed by using only AND gate and NOT gates. Since this circuit uses diodes and transistor, it is called Diode-Transistor Logic (DTL) NOR gate. Implementation of NOR Gate: Positive NOR gate may be implemented by putting transistor NOT gate at the output of a diode OR gate as shown in figure 3. Figure 3(a) gives the circuit symbol and Boolean expression for NOR gate while Figure 1(b) gives the two-input truth table.

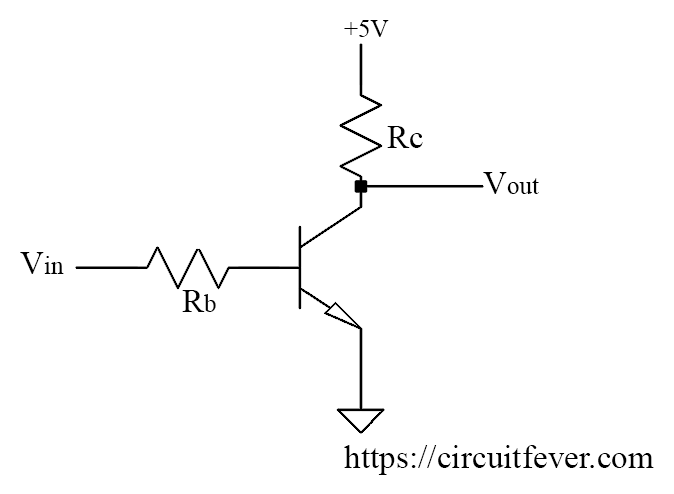

This forms the three-input positive NAND gate using DTL logic.Īn OR gate immediately followed by a NOT gate constitutes the OR-NOT or NOR gate. Thus, the circuit of figure may be rearranged placing NOT gate immediately after the AND gate to yield the NAND gate of figure 2. Implementation of NAND Gate: The NAND gate may be easily implemented by putting a transistor logic NOT gate immediately at the output of a diode AND gate.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed